Advanced Semiconductor Engineering, Inc. (ASE), AMD, Arm, Google Cloud, Intel Corporation, Meta, Microsoft Corporation, Qualcomm Incorporated, Samsung, et Taiwan Semiconductor Manufacturing Company ont annoncé aujourd’hui la création d’un consortium sectoriel qui établira une norme d’interconnexion de puce à puce, favorisant ainsi un écosystème ouvert de puces fragmentées.

Ce communiqué de presse contient des éléments multimédias. Voir le communiqué complet ici : https://www.businesswire.com/news/home/20220302005256/fr/

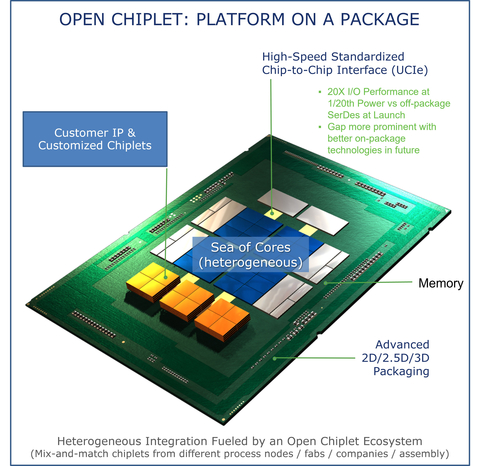

UCIe Open Chiplet: Platform on a Package (Graphic: Business Wire)

L’organisation, qui représente un écosystème diversifié comprenant plusieurs segments de marchés, répondra aux demandes des clients, en faveur d’une intégration plus personnalisable au niveau du paquet ; elle reliera, dans cet objectif, les meilleurs protocoles et interconnexions de puce à puce, à partir d’un écosystème multifournisseur et interopérable.

La spécification Universal Chiplet Interconnect Express (UCIe) est désormais disponible

Les sociétés fondatrices ont également ratifié la spécification UCIe, norme sectorielle ouverte, conçue pour établir une interconnexion universelle au niveau du paquet. La spécification UCIe 1.0 couvre la couche physique I/O de puce à puce, les protocoles de puce à puce, et la pile logicielle, qui s’appuient sur les normes sectorielles bien établies, PCI Express® (PCIe®) et Compute Express Link™ (CXL™). La spécification sera disponible pour les membres de l’UCIe, et téléchargeable sur le site Web.

Ouverture des adhésions

Les sociétés fondatrices possèdent de vastes compétences sectorielles, et incluent les principaux fournisseurs de services cloud, fonderies, FEO de systèmes, fournisseurs de PI en silicium, et concepteurs de puces, s’apprêtant à finaliser leur constitution en tant qu’organisme de normalisation ouvert. Une fois la nouvelle organisation sectorielle UCIe constituée, dans le courant de l’année, les sociétés membres commenceront à travailler sur la technologie UCIe de nouvelle génération, notamment en définissant le format, la gestion, et le renforcement de la sécurité des puces fragmentées, ainsi que d’autres protocoles essentiels. Pour en savoir plus sur les opportunités d’adhésion, veuillez contacter admin@UCIexpress.org.

Ressources :

À propos de l’Universal Chiplet Interconnect Express (UCIe)

L’Universal Chiplet Interconnect Express (UCIe) est une spécification ouverte qui définit l’interconnexion entre les puces fragmentées au sein d’un paquet, favorisant ainsi un écosystème ouvert de puces fragmentées, et une interconnexion universelle au niveau du paquet. Advanced Semiconductor Engineering, Inc. (ASE), AMD, Arm, Google Cloud, Intel Corporation, Meta, Microsoft Corporation, Qualcomm Incorporated, Samsung, et Taiwan Semiconductor Manufacturing Company créent une organisation de normes industrielles ouvertes, visant à promouvoir et développer la technologie, et d’établir un écosystème mondial soutenant la conception de puces fragmentées. Pour en savoir plus, rendez-vous sur www.UCIexpress.org.

PCI-SIG, PCI Express et PCIe sont des marques déposées de PCI-SIG. Compute Express Link™ et CXL™ Consortium sont des marques déposées du Compute Express Link Consortium. Toutes les autres marques commerciales appartiennent à leurs propriétaires respectifs.

Déclarations de soutien des fondateurs de l’Universal Chiplet Interconnect Express (UCIe) (entreprises classées par ordre alphabétique)

Advanced Semiconductor Engineering, Inc. (ASE)

« L’ère des puces fragmentées a véritablement commencé, et encourage le secteur à évoluer, en passant d’une pensée axée sur le silicium à une planification au niveau du système, et axée essentiellement sur la co-conception de CI et de paquets. Nous sommes persuadés que l’UCIe jouera un rôle crucial dans le renforcement des efficiences de l’écosystème, en réduisant les délais et les coûts de développement, grâce à des normes ouvertes favorisant les interfaces entre les différentes PI au sein d’un écosystème multifournisseur, ainsi qu’à l’utilisation d’interconnexions avancées au niveau du paquet. Il est largement admis dans le secteur, que l’intégration hétérogène contribuera à commercialiser des conceptions basées sur des puces fragmentées. Grâce au savoir-faire d’ASE dans les domaines de l’emballage, l’assemblage et les technologies de plateformes d’interconnexion, nous fournirons à l’UCIe une perspective significative permettant de garantir que les prochaines normes sont réalisables, et qu’elles s’accompagnent de coûts de fabrication et de performances commercialement viables pour la fabrication au niveau du paquet », a déclaré le

Dr Lihong Cao, directeur de l’Ingénierie et du Marketing technique, chez ASE, Inc.

AMD

« AMD est fière de poursuivre sa longue tradition quant au soutien des normes sectorielles qui favorisent des solutions innovantes en réponse aux besoins changeants de ses clients. En tant que chef de file dans le domaine de la technologie des puces fragmentées, nous nous réjouissons de la création d’un écosystème de puces fragmentées, multifournisseur, qui permettra une intégration tierce personnalisable. La norme UCIe constituera un facteur clé pour stimuler l’innovation des systèmes, en tirant parti des moteurs de calcul et accélérateurs hétérogènes qui permettront de créer les meilleures solutions en termes de performance, de coût et d’efficacité énergétique », a souligné

Mark Papermaster, vice-président exécutif, et directeur technologique, chez AMD

Arm

« L’interopérabilité est essentielle pour éliminer la fragmentation au sein de l’écosystème Arm, et dans l’ensemble du secteur. En collaborant avec d’autres leaders de l’informatique, Arm s’engage à contribuer au développement des normes et spécifications telles que l’UCIe, afin de créer les conceptions de système, du futur », a indiqué

Andy Rose, architecte de systèmes en chef, et membre, Arm

Google Cloud

« Un écosystème de puces fragmentées, ouvert et normalisé constitue un catalyseur important, apte à promouvoir les conceptions de Système sur puce (Systems on Chip, SoC) en tant que point d’intégration d’un système optimisé. Google Cloud est ravie de participer à la norme Universal Chiplet Interconnect Express, afin de participer au développement d’un marché de puces fragmentées multifournisseur et interopérable, au profit du secteur », a confié

Partha Ranganathan, membre et vice-président de Google

Intel Corporation

« L’intégration de multiples puces fragmentées dans un paquet, en vue de proposer des produits innovants sur tous les segments de marché, constitue non seulement l’avenir du secteur des semiconducteurs, mais un pilier de la stratégie IDM 2.0 d’Intel. Il est essentiel de bénéficier à terme, d’un écosystème ouvert de puces fragmentées, au sein duquel plusieurs partenaires sectoriels clés travaillent ensemble via le Consortium UCIe, à la réalisation d’un objectif commun consistant à transformer la manière dont le secteur délivre de nouveaux produits, et continue d’honorer la promesse de la loi de Moore », a déclaré

Sandra Rivera, vice-présidente exécutive, chez Intel Corporation, et directrice générale des Centres de données et de l’IA

Meta

« Meta est ravie de rejoindre l’UCIe en tant que membre fondateur, afin de créer et promouvoir les interconnexions de puce à puce, normalisées. Meta a d’ores et déjà engagé le développement de l’écosystème, afin de promouvoir les SOC basés sur des puces fragmentées, via l’Open Compute Project (OCP), et la Société se réjouit de collaborer avec d’autres leaders du secteur, dans le cadre du consortium UCIe, pour encourager la réussite actuelle et future dans ce domaine », a indiqué

Vijay Rao, directeur de la division Technologie et stratégie, chez Meta

Microsoft Corporation

« Microsoft rejoint l’organisation sectorielle, UCIe, afin d’accélérer le rythme de l’innovation dans les centres de données, et promouvoir de nouvelles avancées en matière de conception en silicium. Nous sommes impatients de combiner les efforts de l’organisation avec nos propres accomplissements, afin de favoriser des améliorations de la fonction échelon en matière d’architecture en silicium, au bénéfice de nos clients », a confié le

Dr Leendert van Doorn, ingénieur émérite au sein de la division Azure, chez Microsoft

Qualcomm Incorporated

« Qualcomm est ravie que le secteur se rassemble pour créer l’UCIe qui devrait faire avancer la technologie des puces fragmentées, laquelle est particulièrement importante pour résoudre les défis liés à nos systèmes de semiconducteurs, de plus en plus complexes », a affirmé le

Dr Edward Tiedemann, vice-président principal de l’Ingénierie, chez Qualcomm Technologies, Inc.

Samsung

« Samsung considère que la technologie des puces fragmentées sera indispensable pour fournir des gains de performance aux systèmes informatiques, à l’heure où les nœuds de traitement continuent de se développer, les puces contenues dans chaque paquet communiquant finalement via un seul et même langage. Nous sommes convaincus que le Consortium UCIe promouvra un écosystème de puces fragmentées, dynamique, et instaurera le cadre d’une interface à normes ouvertes, viable, à l’échelle du secteur. En tant que fournisseur complet de solutions destinées à la mémoire, à la logique et à la fonderie, Samsung entend s’inscrire à la tête des efforts du consortium afin d’identifier les meilleurs moyens d’améliorer la performance des systèmes, grâce à la technologie des puces fragmentées », a souligné

Cheolmin Park, vice-président de l’équipe de Planification des produits de mémoire, chez Samsung Electronics

Taiwan Semiconductor Manufacturing Company

« TSMC est ravie de participer à ce consortium à l’échelle du secteur, qui permettra d’étendre l’écosystème de l’intégration au niveau du paquet. TSMC fournit plusieurs technologies de silicium et d’emballage, offrant de multiples possibilités de mise en œuvre pour les appareils UCIe hétérogènes », a commenté

Lee-Chung Lu, membre, et vice-président de la Conception et de la Plateforme technologique, de TSMC

Le texte du communiqué issu d’une traduction ne doit d’aucune manière être considéré comme officiel. La seule version du communiqué qui fasse foi est celle du communiqué dans sa langue d’origine. La traduction devra toujours être confrontée au texte source, qui fera jurisprudence.

Consultez la version source sur businesswire.com : https://www.businesswire.com/news/home/20220302005256/fr/