Du RISC-V chez Scaleway : quelle offre pour commencer ?

Une offre de serveurs RISC-V émerge chez Scaleway. Quels en sont le positionnement et les caractéristiques ?

Parler de souveraineté alors qu’on utilise un processeur chinois ? L’arrivée de serveurs RISC-V chez Scaleway a suscité des questions à ce sujet.

Le directeur R&D a eu tôt fait de répondre.

Je sais pas si tu nous as bien lu. On te dit pas que l’offre est souveraine, on te dit que c’est une opportunité pour qu’un jour ça le soit.

Faut savoir faire des compromis pour avancer.

Je suis sûr que tes processeurs sont produits dans le jura.— Seblu (@seblu84) February 29, 2024

On est, quoi qu’il en soit, encore loin d’une offre à grande échelle. Elle est en accès anticipé, donc sans garantie de fiabilité, de stabilité, d’intégrité, etc. Au menu, un modèle d’instance, disponible dans la zone FR-PAR-2, avec la configuration et les prix suivants :

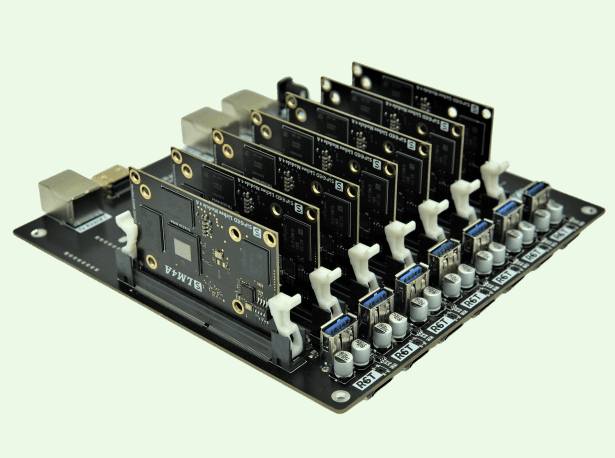

Châssis découpés au laser, lames imprimées en 3D, composants soudés à la main… Scaleway insiste sur l’assemblage « maison » des serveurs.

Rackage à DC5 terminé. Câblage #Atari. Les DEL sont cramptés. Une belle densité de 672 serveurs par rack. La date de lancement est fixée. On peut partir en vacances. cc @Scaleway_fr #dedibox #baremetal pic.twitter.com/yQGIJ3C7sG

— Seblu (@seblu84) February 16, 2024

Sous le capot, il y a des clusters de cartes Sipeed : des Lichee fondées sur le SoC T-Head 1520 d’Alibaba (4 cœurs CPU à 1,85 GHz, GPU, VPU et NPU).

Niveau prix faut comparer avec les types d’instance GCP et Azure avec lesquels ils se comparent. Après c’est du « labs » avec des SLAs idoines. Maintenant oui d’un point de vue d’hobbyiste c’est plus cher que mon auto-hébergement :)

— Thomas Jardinet (@ThomasJardinet) March 1, 2024

Quelles performances pour ces serveurs RISC-V ?

En attendant l’accès à la console série pour installer ses propres OS, on peut choisir entre Alpine Linux, Debian et Ubuntu. Les réseaux privés ne sont pas encore pris en charge, au contraire des adresses IP flexibles. Scaleway fournit pour le moment du 100 Mb/s, même si les cartes supportent le gigabit.

bootet up my first risc-v server :-) pic.twitter.com/fgILR5fDOb

— konkretor (@konkretor) February 29, 2024

#scaleway offers #RISCV metal instances with @alpinelinux!

It appears to be relatively vanilla alpine edge with a custom kernel.https://t.co/VZo5E9B1cY

— @ncopa@fosstodon.org (@n_copa) February 29, 2024

Scaleway annonce une conso de 0,96 et 1,9 W par cœur CPU. Il communique des performances sur trois benchmarks :

- Geekbench 6 CPU

À 380 points, les performances dépassent celles de l'instance Dedibox Start-3-S en Intel C2350 dual-core (256 points). Mais pas celles de la Dedibox Start-1-M en Intel C2750 octa-core (1112 points).

- PostgreSQL

1356 transactions par seconde, c'est du même ordre que l'instance GCP e2-small x64 (1409).

- Sysbench CPU

À 6432 événements par seconde, l'écart est net avec l'instance GCP (797). La configuration Scaleway la plus proche parmi celles testées est la Dedibox Start-1-M (4308).

En retrait sur ces benchmarks, la carte VisionFive 2 de StarFive l'est moins sur certains comparatifs tiers. Dans l'un d'entre eux, elle s'en sort mieux que la config Scaleway sur UnixBench 5.1.3, en monocœur comme en multicœur.

Les résultats ne sont cependant pas uniformes. Les instances de Scaleway sont, par exemple, nettement plus performante sur Whestone en double précision. C'est le contraire sur la création de processus et le débit Execl.

I'll keep using my VisionFive 2 at home. But good to know there are already some RISC-V server offerings out there!

— Adrián Arroyo Calle (@aarroyoca) February 29, 2024

Dans la dynamique du Chips Act

À travers cette initiative, Scaleway se veut un « activateur » de l'écosystème RISC-V. Il entrevoit, avec cette architecture ouverte, « l'émergence d'acteurs locaux permettant à terme aux nations de contrôler la fabrication de leurs processeurs ».

En toile de fond, le Chips Act (loi européenne sur les semi-conducteurs). Entré en vigueur en septembre 2023, ce règlement institue une initiative Chips for Europe. Celle-ci comprend cinq objectifs opérationnels. Les quatre premiers sont à la charge d'une entreprise commune « Semi-conducteurs » (ex-« Technologies-clés »).

L'initiative Chips for Europe bénéficie de financements à travers Horizon Europe. Une enveloppe lui est également dédiée dans le cadre du programme pour une Europe numérique. Le Chips Act la fixe à 1,575 milliard d'euros sur la période 2021-2027.

Le recours à RISC-V est l'un des moyens envisagés pour développer des capacités de conception intégréesà grande échelle. Un rapport d'experts remis en septembre 2022 à Bruxelles sur la question du hardware open source est venu appuyer cette approche en identifiant les débouchés pertinents. Parmi eux, le HPC.

Dans la foulée, EuroHPC a organisé un appel à projets axé sur le développement de technologies et l'adaptation de l'existant pour permettre d'y intégrer des composants RISC-V. Il s'agissait aussi de définir des standards et des spécifications d'interfaces, tout en assurant que la propriété intellectuelle « reste en Europe ».

Entre autres projets européens, De-RISC (Dependable Real-Time Infrastructure for Safety-critical Computer) cible l'aéronautique et l'aérospatiale. Thales emmène le consortium qui le porte. Objectif : productiser un SoC RISC-V de l'entreprise britannique Cobham Gaisler et adapter l'hyperviseur XtratuM de Fent Innovative Software Solutions.

SoC Cobham Gaisler également pour Trisat-R. Ce projet développé avec l'université de Maribor (Slovénie) a abouti à la mise en orbite d'un nanosatellite pour mesurer les rayonnements ionisants.

Suis curieux de suivre l’expérimentation et surtout ce qui tourne autour de l’installation ’bare metal’ pour en faire un mini cluster K8S.

Vais m’en prendre 2-3 pour jouer.

Mais suis curieux de mixer ca avec leur offre ‘node as commodity’, mais sans PaaS (sorry clever cloud ).

— Vincent Nonnenmacher (@solipticid) March 1, 2024

Illustration © Sipeed